ดีฟลิปฟล็อป

บทความนี้ได้รับแจ้งให้ปรับปรุงหลายข้อ กรุณาช่วยปรับปรุงบทความ หรืออภิปรายปัญหาที่หน้าอภิปราย

|

ดีฟลิปฟล็อป เป็นฟลิปฟล็อปที่ทำงานตามตารางสถานะถัดไปด้านล่าง ฟลิปฟล็อปชนิดนี้เป็นฟลิปฟล็อปที่ถูกนำมาใช้มากกว่าชนิดอื่น เพราะเข้าใจระบบการทำงานง่าย เนื่องจากดีฟลิปฟล็อปมีสถานะถัดไปเดียวกับอินพุตที่เข้ามา ฟลิปฟล็อปชนิดนี้จึงถูกนำไปสร้างเป็นเรจิสเตอร์ และเครื่องสถานะจำกัดอื่นๆ ตารางสถานะถัดไปของเจเคฟลิปฟล็อป

| 0 | 0 |

| 1 | 1 |

ตารางสภาวะกระตุ้น

| 0 | 0 | 0 |

| 1 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 1 | 1 |

การใช้งาน[แก้]

การใช้งานของดีฟลิปฟล็อปโดยทั่วไปจะมี 2 ประเภท คือ

- ใช้เป็นตัวเก็บค่าข้อมูล เรียกว่า (Data-latch) ข้อมูลจะถูกเก็บใว้จนกว่าจะมีพัลส์ลูกใหม่เข้ามาและจะคงค่าข้อมูลไว้แม้ว่าข้อมูลที่ อินพุตเข้าไปจะเปลี่ยนแปลงกลับไปกลับมา

- ใช้ในการหน่วงสัญญาณ โดยสัญญาณที่เข้ามาใน ดี ฟลิปฟล็อปจะไม่ถูกส่งไปทางเอาต์พุตและจะต้องรอสัญญาณพัลส์อีกหนึ่งลูกที่เข้ามา

แผนภาพบล็อกของดีฟลิปฟล็อปแสดงการทำงานขอบขาขึ้นและขาลงตามลำดับ

การทำงานของดีฟลิปฟล็อป[แก้]

ฟลิปฟล็อปจะมีสัญญาณเข้า 2 อินพุต คือ อินพุตข้อมูล(D) และ อินพุตควบคุม(G) โดยถ้าหากให้ G เป็นลอจิก" 1" และให้ G ได้รับสัญญาณลอจิก "1" จะทำให้เอาต์พุต Q เป็น "1" และ ฟลิปฟล็อปจะแลตซ์ค่านี้ตลอดจนกว่าอินพุต D จะมีค่าใหม่เข้ามาทางขา G อีกครั้ง

ภาพลักษณะการทำงานของ D flip-flop

เวลาการตรวจสอบเงื่อนไข จะสั้นกว่าแลตซ์ที่ทำงานตลอดช่วงที่ EN เป็น 1 เนื่องจากการทำงานของฟลิปฟล็อปนั้นจะทำงานที่ขอบนาฬิกา

ภาพสัญญาณนาฬิกา

ฟลิปฟล็อปแบบกระตุ้นด้วยขอบสัญญาณ[แก้]

การกระตุ้นของสัญญาณฟลิปฟล็อปจะเป็นการกระตุ้นด้วยระดับแรงดัน ที่เรียกว่า Level Trigger บางครั้งฟลิปฟล็อปจะทำงาน ในช่วงเวลาสั้นๆ โดยฟลิปฟล็อปจะเปลี่ยนสถานะเมื่อสัญญาณควบคุมเปลี่ยนลอจิก "0" เป็นลอจิก "1" เรียกว่าการกระตุ้นด้วยอบขาขึ้น หรือ ถ้าเมื่อสัญญาณนาฬิกาเปลี่ยนจากลอจิก"1" เป็นลอจิก "0" เรียกว่า การกระตุ้นด้วยขอบขาลง โดยฟลิปฟล็อปประเภทนี้จะนิยมใช้ในวงลิจิกที่ต้องการความเร็วสูงในระบบคอมพิวเตอร์

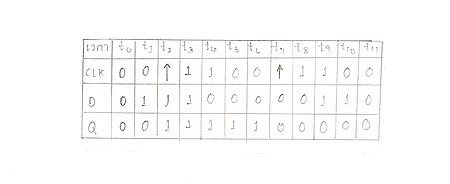

Timing diagram การคิดแบบ delay คือการที่ Q มันจะไม่เปลี่ยนแปลงโดยทันทีสัญญาณขาขึ้นจะผ่านไปได้ระยะหนึ่งก่อน

หน้าที่ฟลิปฟล็อปจะถูกกระตุ้น

ภาพการตรวจสอบค่า D ที่คิดแบบ delay

การเปลี่ยนสถานะของ D flip-flop

เมื่อได้รับอินพุตต่างๆโดยเรียงตามลำดับเวลาการได้รับอินพุต D ฟลิปฟล็อปจะถูกกระตุ้นผลก็คือเอาต์พุตจะเปลี่ยนตามอินพุตแต่ช่วงเวลาอื่นๆ D flip-flop จะคงค่าเดิมไว้โดยเรียงลำดับเวลาการได้รับอินพุต ในช่วงเวลา t2และ t10